- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC18C858T-I/PT (Microchip Technology)IC MCU OTP 16KX16 CAN 80TQFP

PIC18CXX8

DS30475A-page 104

Advanced Information

2000 Microchip Technology Inc.

8.8

PORTH, LATH, and TRISH Registers

PORTH is a 5-bit wide, bi-directional port available only

on the PIC18C858 devices. The corresponding Data

Direction register is TRISH. Setting a TRISH bit (=1)

will make the corresponding PORTH pin an input (i.e.,

put the corresponding output driver in a hi-impedance

mode). Clearing a TRISH bit (=0) will make the corre-

sponding PORTH pin an output (i.e., put the contents

of the output latch on the selected pin).

Read-modify-write operations on the LATH register

read and write the latched output value for PORTH.

Pins RH0-RH3 on the PIC18C858 are bi-directional I/O

pins with ST input buffers. Pins RH4-RH7 on all devices

are multiplexed with A/D converter inputs.

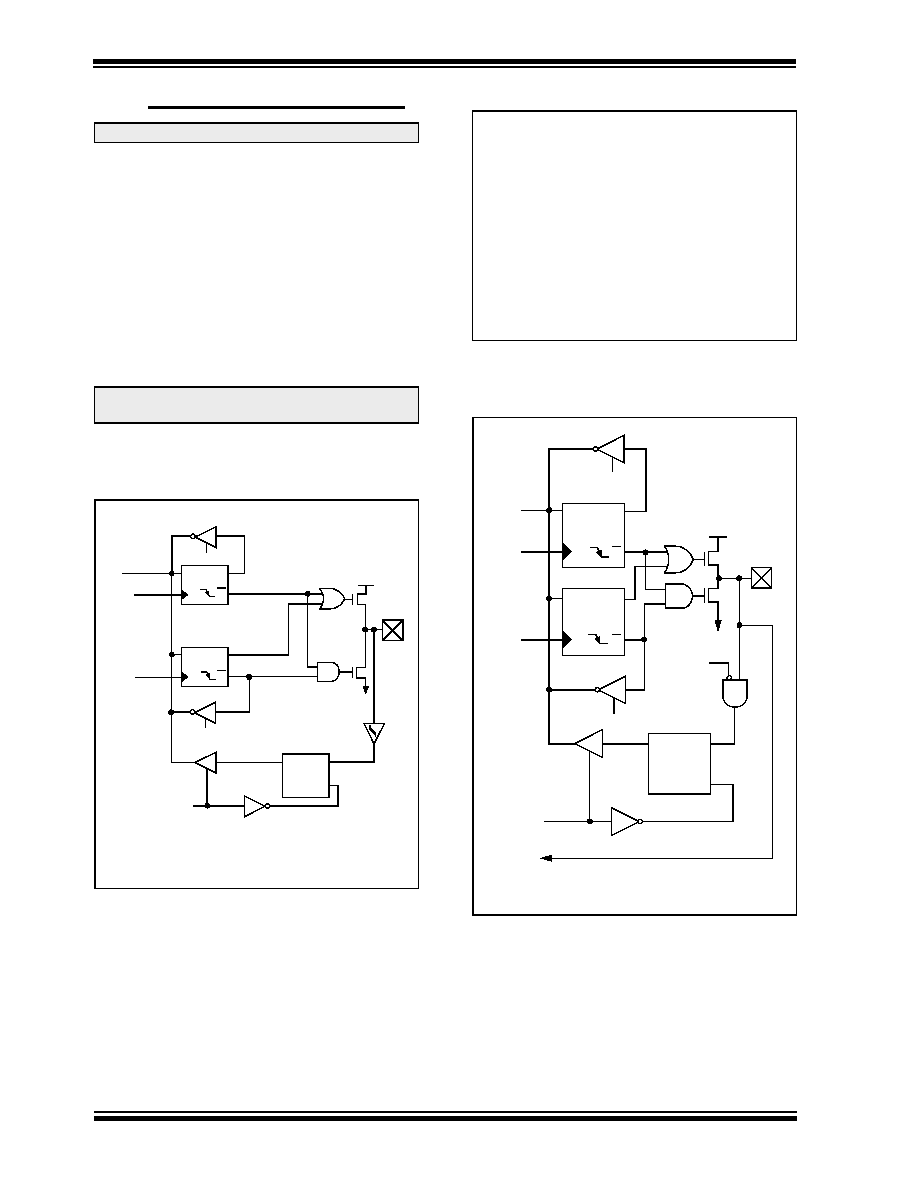

FIGURE 8-16: RH3:RH0 PINS BLOCK

DIAGRAM

EXAMPLE 8-8:

INITIALIZING PORTH

FIGURE 8-17: RH7:RH4 PINS BLOCK

DIAGRAM

Note:

This port is available on PIC18C858.

Note:

On a Power-on Reset, the RH7:RH4 pins

are configured as inputs and read as ’0’.

Data Bus

WR LATH

WR TRISH

RD

Data Latch

TRIS Latch

RD TRISH

Schmitt

Trigger

Q

D

Q

CK

QD

EN

Q

D

Q

CK

P

N

VDD

VSS

PORTH

I/O Pin

or

WR PORTH

RD LATH

Note:

I/O pins have diode protection to VDD and VSS.

CLRF

PORTH

; Initialize PORTH by

; clearing output

; data latches

CLRF

LATH

; Alternate method

; to clear output

; data latches

MOVLW

0x0F

;

MOVWF

ADCON1

;

MOVLW

0xCF

; Value used to

; initialize data

; direction

MOVWF

TRISH

; Set RH3:RH0 as inputs

; RH5:RH4 as outputs

; RH7:RH6 as inputs

Data

Bus

Q

D

Q

CK

Q

D

Q

CK

QD

EN

P

N

WR LATH

WR TRISH

Data Latch

TRIS Latch

RD TRISH

RD PORTH

VSS

VDD

I/O Pin

Analog

Input

Mode

ST

Input

Buffer

To A/D Converter

RD LATH

or

WR PORTH

Note:

I/O pins have diode protection to VDD and VSS.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/PT

IC MCU OTP 16KX16 CAN 64TQFP

PIC16LC717T-E/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16C771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC770T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC717T-I/SO

IC MCU OTP 2KX14 A/D PWM 18SOIC

PIC16LC771T/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

相关代理商/技术参数

PIC18F1220-E/ML

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/P

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SO

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SS

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/ML

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/P

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SO

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SS

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT